DDS – функциональный генератор с «джамперным» управлением на ПЛМ

Вашему вниманию предлагается функциональный генератор, разработанный в качестве примера использования технологии DDS (Direct Digital Synthesizer) на базе ПЛМ EPM3064ALC44-10 фирмы Altera (стоимость ПЛМ – около 2$). Параметры прибора следующие:

- Форма выходного сигнала:

- синусоидальный

- треугольный

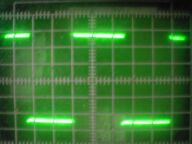

- прямоугольные импульсы

- Амплитуда выходного сигнала – около 1В

- Установка частоты: 0 Гц -1.5 МГц с дискретностью около 3 Гц

- Разрядность выходного ЦАП – 6

- Управление режимом и частотой – при помощи ряда джамперов

Возможные вариации (при изменении набора функций и/или применении ПЛМ большего объема/быстродействия):

- Увеличение разрядности ЦАП до 7 или 8

- Уменьшение шага установки частоты до 1Гц и менее

- Увеличение максимальной генерируемой частоты

- Подключение к микроконтроллеру

- Управление PLL-генератором – например, в малошумящем синтезаторе частоты КВ трансивера

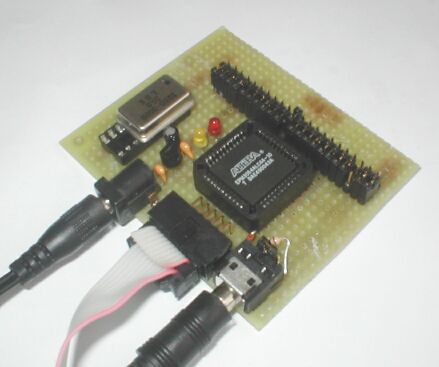

Напряжение питания стабилизируется микросхемой 78L03. Двухрядный 10-контактный разъем предназначен для подключения программатора ByteBlaster. Режим работы и частота задаются джамперами. В качестве опорного генератора используется кварцевый генератор (частота 25 МГц). 6-разрядный резисторный ЦАП собран по классической схеме R-2R, на выходе которого необходимо установить ФНЧ (схема которого определяется требованиями к чистоте спектра сигнала) .

22-разрядный сумматор adder вычисляет сумму входного вектора in[21..0] (из них 19 разрядов выведены на джамперы, на остальные 2 подается логический «0») и содержимого регистра reg. Входной сигнал iclk, частота которого поделена на 2 триггером, защелкивает очередную сумму sum[21..0] в регистре. Таблица functab7x6 формирует 6-разрядный выходной код dac[5..0] (подаваемый на ЦАП) из входного, подключенного к 7 старшим разрядам q[21..15] регистра. Входы sinsaw и square выбирают форму синтезируемого сигнала: синусоидальный, треугольный или прямоугольные импульсы.

Приведенная выше схема нарисована в графическом редакторе системы MAX+PLUS, а ее функциональные элементы реализованы на языке программирования AHDL.

ВременнОй анализ схемы в системе MAX+PLUS (Registered Performance) показывает, что для применяемой микросхемы EPM3064ALC44-10 внутрисхемные временные задержки (в основном, в сумматоре) могут составить примерно 90 нс. Это ограничивает тактовую частоту схемы на уровне примерно 11 МГц. В описанной схеме эта частота составляет 12.5 МГц, что несколько выше допустимой, однако схема работает нормально.

Для расчета коэффициента, определяющего положение 19 джамперов для заданной выходной частоты, воспользуемся формулой:

K = F*(2^22)/(25000000/2) ≈ F*0.33554432,

здесь F – необходимая частота в Гц, 22 – разрядность сумматора, 25000000 – частота генератора, Гц.

Для частоты 1 кГц, получим K = 335.54432 ≈ 336 или 1010100002 в двоичной форме.

По обратной формуле

F = K*(25000000/2)/(2^22) = K*2.9802322

вычислим точное значение частоты для коэффициента K=336: F=336*2.9802322=1001.3580322 Гц.

Максимальная генерируемая частота: Fmax = 11111111111111111112 * 2.9802322 ≈ 1.562497 МГц. Если 3 старших разряда in[21..19] сумматора (см. рис. 4) также вывести на джамперы, эта частота составит 6.25 МГц.

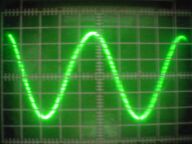

Спектрограмма синусоидального сигнала с частотой 1.5 кГц (программа SpectraLab). Испытания показывают, что уровень самой сильной гармоники для низкочастотного синусоидального сигнала составляет около -50 дБ.

Комплект схем и программ для MAX+PLUS:

Источники:

Murray Greenman, ZL1BPU. A Sine/Noise/Pulse and Sweep Generator.

ПЛМ фирмы Altera. www.altera.com

А.П. Антонов. Язык описания цифровых устройств AlteraHDL. Практический курс. -М.:ИП РадиоСофт, 2002.

Денис Нечитайлов (UU9JDR)